120 Questões de concurso encontradas

Página 9 de 24

Questões por página:

A partir das informações apresentadas e considerando os aspectos de hardware e software relacionados, julgue o item que se segue.

Para a resolução do conversor A/D e para a faixa de entrada citadas, a menor variação de tensão que pode ser distinguida pelo conversor é de aproximadamente 1,22 mV.

Considerando operação ideal em regime de condução contínua, a tensão de saída (vs) do conversor step-up é relacionada à tensão de entrada (ve) por vs = ve/1-D, em que D é o ciclo de trabalho (duty cycle).

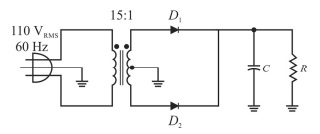

A fonte de alimentação implementada pelo circuito a seguir utiliza um transformador com secundário de tomada central e razão de transformação de 15:1 entre o primário e cada metade do secundário (da tomada central até uma das extremidades), o que resulta em uma razão de 7,5:1 entre o primário e a tensão total entre as extremidades do secundário. O enrolamento primário recebe uma tensão alternada de 110 VRMS/60 Hz. O circuito conta com dois diodos retificadores comuns (D1 e D2), com queda típica de 0,7 V em condução, um capacitor de filtragem de 1.000 μF e um resistor de carga de 100 Ω.

A partir dessas informações, julgue o item seguinte.

A tensão média sobre o resistor de carga R é maior que 11 V.

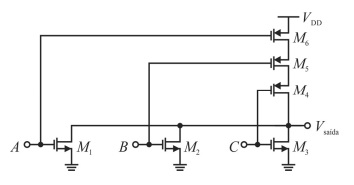

Com base no circuito precedente, que utiliza transistores MOSFET em tecnologia CMOS, julgue o item subsecutivo.

O circuito utiliza três transistores PMOS conectados em série e três transistores NMOS conectados em paralelo, formando uma arquitetura típica de uma porta NAND de três entradas.

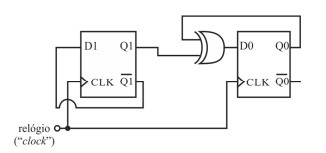

Considerando o circuito precedente, que utiliza dois flip-flops tipo D acionados por borda de subida do sinal de relógio, julgue o item a seguir, assumindo que qualquer controle de PRESET ou de CLEAR esteja adequadamente configurado para permitir operação contínua.

Para os flip-flops corretamente inicializados, se o circuito operar com pulsos de clock contínuos, os estados das saídas (Q1, Q0) a cada borda de subida do relógio evoluirão de forma cíclica na ordem 00 → 10 → 01 → 11 → 00 → ... .